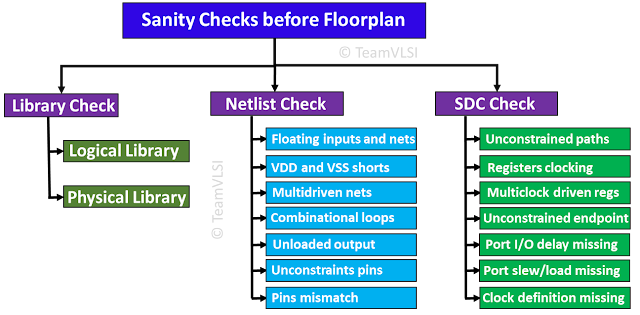

Sanity checks are an important step for physical design engineers to make sure that the inputs received for physical design are correct and consistent. Any issues in the input files may cause problems in the later stages. So it is important to perform the sanity checks in the initial stage that is when the design is loaded in PnR tool and before the start of the floorplan.

Here is a list of checks which must be performed before the floorplan of design.

|

Figure-1: Sanity checks before floorplan |

Library Check:

In library check, basically, we validate the libraries before starting the physical design by checking the consistency between the physical and logical library. It also checks the quality of both libraries and reports the error if any. The cells used in the design must be present in the logical as well as in the physical library.

Innovus commands:

checkDesign -physicalLibrary

ICC2 commands:

Performs consistency checks between the logical and physical library, across the logical library and within the physical library.

Netlist Check:

Netlist must be checked for consistency. This check analyzes the currently loaded netlist and reports the inconsistency if any. Netlist check mainly checks:

- Floating input pins and nets

- No direct connection between VDD and VSS

- Multidriven nets

- combinational loops

- Unloaded outputs

- Uncontraints pins

- Mismatch pin count between instance and reference

Innovus command:

checkDesign -netlist

ICC command:

check_design

SDC Check:

SDC file must be checked before start the design. Some of the common issues in SDC file are as follow.

- Unconstrained path

- Clock is reaching to all synchronous elements

- Multiclock driven registers

- Unconstrained endpoint

- Input/output delay missing for a port

- Slew or load constraint missing for a port

- Missing clock definition

Innovus command:

check_timing

ICC command:

check_timing

Thank you!