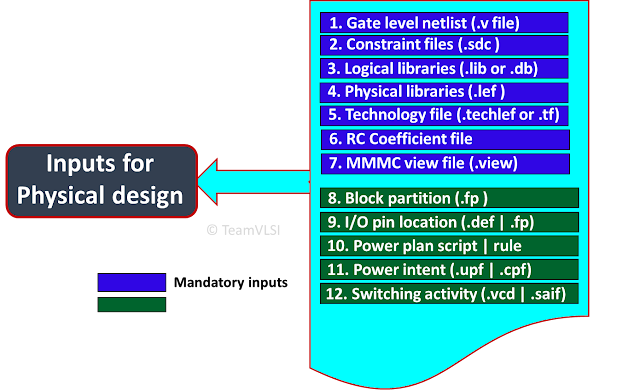

In this article, we will discuss what are the inputs required to begin the physical design. In the previous article, we discussed the physical design flow and sanity checks before the floorplan. Inputs required for physical design can be categorised broadly into two types. Some inputs are mandatory in all the cases but some are required for a specific purpose. Figure-1 shows the list of inputs required for physical design and categorises the mandatory and optional inputs.

|

|

|

|

In the set input files, the first set is design-related files which contain Gate level netlist file and design constraint files. These files come from the synthesis team. Let’s briefly see the content of these files.

Gate level netlist:

This is the synthesized netlist. The synthesis team performs synthesis on RTL code with the standard cell libraries and constraints and converts the RTL code into the gate-level netlist based on available standard cells. This file contains all the instances of design and their connection.

Constraint file:

A Constraint file is popularly known as an SDC file by its extension of the file. It contains basically,

-

- Units (Time, Capacitance, Resistance, Voltage, Current, Power)

- System interface (Driving cell, load)

- Design rule constraints (max fanout, max transition)

- Timing constraints (Clock definitions, clock latency, clock uncertainty, input/output delay)

- Timing exceptions (Multi-cycle and false paths)

A detailed description of the SDC file is explained here

Now some inputs are required which are related to standard cell libraries. These files are provided by the standard cell library vendor and these files are as follows.

Logical libraries:

The logical library is also called a timing library or functional library or power library as it contains the functionality, time and power information of cells. This file contains basically the following information of the standard cells or macros.

- Timing details of the standard cells / macros ( delay, transitions)

- Setup and hold time of standard cells / macros

- Functionality details of standard cells /macros

- Area of standard cells / macros

- Pin directions and capacitance

- Leakage power of standard cells / macros

The logical libraries could be either in liberty format .lib file for Cadence tool or in the form of .db file for Synopsys tool. There are different logical files for different PVT corners. Liberty file is created by doing the standard cell library characterization, so this file is provided by the standard cell library vendor.

Physical libraries:

The physical library contains the abstract view of the layout for standard cells and macros. LEF file basically contains:

- Size of the cell (Height and width)

- Symmetry of cell

- Pins name, direction, use, shape, layer

- Pins location

Physical libraries are in Library Exchange Format (.lef) for the Cadence tools or .CELL and .FRAM form for Synopsys tool. This file is provided by the standard cell library vendor.

Technology file:

The technology library is the most critical input to the physical design tool. The technology library contains detailed information about all the metal layers, vias and their design rules. This file is in ASCII format and basically contains the following information:

- Manufacturing grid

- Layers name (poly | contact | metal1 |via2 )

- Types and the direction of the metal

- Pitch

- Width

- Spacing

- Resistance (per square unit)

The technology file used by the Cadence tool is .techlef format and .tf format by Synopsys tool.

RC coefficient file:

TLU file is a short form of “Table Look-Up” used for RC estimation and extraction or we use QRC file or cap table for the same.

MMMC view file:

Multi-Mode Multi-Corner file is used to generate different analysis views based on different delay corners and constraints modes. Delay corners are defined on library sets and RC corners. There are various library set files based on voltage and temperature values (like ss, ff, typical).

The above set of files is needed to initiate all the physical designs. Some files format is different for the Cadence tool and Synopsys tool. There are some optional files that might be required especially for block-level PnR implementation. These files are as below.

Block partition:

For block-level PnR, we need a defined core area for the block or block partitions which defines the size and shape of the block. Block shape could be a simple rectangular or a complex rectilinear shape.

Pin def:

For block-level PnR, pin locations have been decided by the Full chip owner and for block-level, we have to use the predecided pin location in order to match the pin locations with other blocks. Generally, it is given in form of a def file. In case of any pin placement issue at the block level, the block owner can inform the person who is placing the pin and if required block owner can also edit the pin placement.

Power plan script:

For block-level PnR, the power plan should be as per the full chip. The power plan has been decided on full chip and in block level, the Power plan should be used as per full chip. A power plan could be given a set of rules or a power plan script (.tcl file).

Power intent (UPF | CPF file):

The power intent file describes which power rails should be routed to individual blocks and when the block should be powered on or shut down. Unified Power Format (.upf) and Common Power Format (.cpf) are two different formats of power intent files. CPF format is used by the Cadence tool and UPF format by the other tools. We must need this file if the block is having a multi-voltage domain.

Switching activity files (VCD | SAIF):

SAIF or VCD file is used basically for the dynamic IR analysis in the Physical design. Dynamic IR analysis provides the Dynamic power drop inside the chip based on the switching activities.

Hello, not sure why you specify that a gds file is mandatory for the PD phase. Did you mean a layermap file instead?

Also, in "RC coefficient file:": QRC or capTable files are also used (depending on the tool and process node)

Thanks,

Yes, rightly said.

Thank You.

Actually gds file is needed only at the time of gds stream out not in the process of Physical design.

Thanks a lot for the catch. I will make the correction.

Done!

Thanks! Last comment (it's a detail but I would specify it): in most recent tech nodes (for Cadence tools), a .techlef is not used anymore. Instead, the information are specified in a .lef file directly.

Alright! Yes there are two parts of LEF file and the first part is tech lef where all the metal layers and rules are defined. For Cadence tool LEF file is only used. But in Synopsys tool a .tf file used for this purpose.

The LEF file definition should be "library exchange Format", not "liberty exchange format"

Thanks for the catch. Correction has done!