In this article, we will discuss a widely used and very popular file used for data exchange from one EDA tool to another tool. Yes, we are going to discuss the Design Exchange Format or DEF file which is having extension .def. In this article, we will discuss the use of the def file, what information this file contains and how the information is arranged in various sections. We will also discuss how can we generate this file.

Introduction:

DEF file is used to represent the Physical layout of an Integrated Circuit (IC) in ASCII format. A DEF file is strongly connected with the Library Exchange Format (LEF) file. So both files are needed for a correct display of physical design. DEF file format was developed by Cadence Design System. Whenever we need to transfer the design database from one EDA tool to another EDA tool for further implementation or analysis, we use the DEF file to transfer the design data. For example IR analysis on PnR database or STA on PnR database we transfer the design database in form of a DEF file.

A DEF file contains the design-specific information of the circuit and it is a representation of the design at any point during the physical design. DEF conveys logical design data and physical design data.

Logical design data includes internal connectivity (represented by netlist), group information and physical constraints. Physical data includes placement location and orientation of components and routing geometry.

Sections:

A standard DEF file contains mainly following sections and order of statement is also important.

- [ VERSION statement ]

- [ DIVIDERCHAR statement ]

- [ BUSBITCHARS statement ]

- [ DESIGN statement ]

- [ TECHNOLOGY statement ]

- [ UNITS statements ]

- [ DIAAREA statement ]

- [ ROW statement ]

- [ TRACKS statement ]

- [ CELLGRID statement ]

- [ VIAS statements ]

- [ NONDEFAULTRULES statement ]

- [ COMPONENTS statement ]

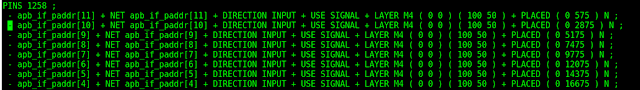

- [ PINS section ]

- [ BLOCKAGE section ]

- [ FILLS section ]

- [ SPECIALNETS section ]

- [ NETS section ]

- [ SCANCHAINS section ]

- [ GROUPS section ]

- [ BEGINEXT section ]

- END DESIGN statement

Here we will take a sample DEF file to describe the various sections of the file.

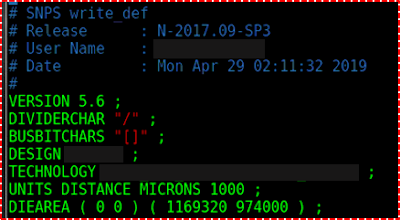

Header statement:

|

| Figure-1: Header part of DEF file |

In the header part, the version of DEF, Design name, Technology name, Units and Dia area are mentioned.

ROW statement:

|

| Figure-2: Row statement in DEF file |

rowName: Specifies the row name for this row.

siteName : Specify the LEF site to use for the row

origX origY : Specify the location of first site in the row

siteOrientation : Specifies the orientation of all sites in the row

Do numX BY numY :

STEP stepX stepY :

Track statement:

Syntax:

[TRACKS [{X | Y} start DO numtracksSTEP space [LAYER layerName…] ;] …]

Example:

|

| Figure-3: Track statement in DEF file |

Description:

{X | Y } start

Do numtracks

Specifies the number of tracks to create for the grid

STEP space:

LAYER layerName

GCell Grid statement:

[GCELLGRID {X start DO numColumns+1 STEP space} … {Y start DO numRows+1 STEP space ;} …]

Example:

|

| Figure-4: Gcell statement in DEF file |

Description:

{X | Y } start :

Do numColumns+1 :

Do numRows+1 :

STEP space:

Via statement:

Example:

|

| Figure-5: Via statement in DEF file |

All vias consist of shapes on three Layers

NDR statement:

NONDEFAULTRULES numRules;

{- ruleName

[+ HARDSPACING]

{+ LAYER layerName

WIDTH minWidth

[DIAGWIDTH diagWidth]

[SPACING minSpacing]

[WIREEXT wireExt]

} …

[+ VIA viaName] …

[+ VIARULE viaRuleName] …

[+ MINCUTS cutLayerNamenumCuts] …

[+ PROPERTY {propNamepropVal} …] …

;} …

END NONDEFAULTRULES

|

| Figure-6: NDR in DEF file |

Description:

•It defines any non-default rules used in this design that are not specified in the LEF file.

•This section can also contain the default rule and LEF nondefault rule definitions for reference.

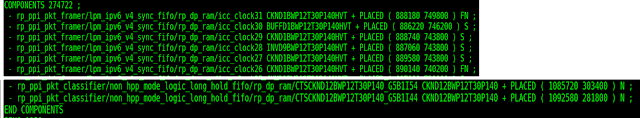

Component section:

COMPONENTS numComps;

[– compNamemodelName

[+ EEQMASTER macroName]

[+ SOURCE {NETLIST | DIST | USER | TIMING}]

[+ {FIXED pt orient | COVER ptorient | PLACED ptorient

| UNPLACED} ]

[+ HALO [SOFT] left bottom right top]

[+ ROUTEHALO haloDistminLayermaxLayer]

[+ WEIGHT weight]

[+ REGION regionName]

[+ PROPERTY {propNamepropVal} …]…

;] …

END COMPONENTS

|

| Figure-7: Component section in DEF file |

Pin section:

Blockage section:

|

| Figure-9: Blockage section in DEF file |

Special net section:

[SPECIALNETS numNets;

[– netName

[ ( {compNamepinName| PIN pinName} [+ SYNTHESIZED] ) ] …

[+ VOLTAGE volts]

[specialWiring] …

[+ SOURCE {DIST | NETLIST | TIMING | USER}]

[+ FIXEDBUMP]

[+ ORIGINAL netName]

[+ USE {ANALOG | CLOCK | GROUND | POWER | RESET | SCAN | SIGNAL | TIEOFF}]

[+ PATTERN {BALANCED | STEINER | TRUNK | WIREDLOGIC}]

[+ ESTCAP wireCapacitance]

[+ WEIGHT weight]

[+ PROPERTY {propNamepropVal} …] …

;] …

END SPECIALNETS]

Example:

|

| Figure-10: Special net section in DEF file |

Net section:

NETS numNets;

[– { netName

[ ( {compNamepinName| PIN pinName} [+ SYNTHESIZED] ) ] …

| MUSTJOIN ( compNamepinName) }

[+ SHIELDNET shieldNetName] …

[+ VPIN vpinName[LAYER layerName] ptpt

[PLACED pt orient | FIXED ptorient | COVER ptorient] ] …

[+ SUBNET subnetName

[ ( {compNamepinName| PIN pinName| VPIN vpinName} ) ] …

[NONDEFAULTRULE rulename]

[regularWiring] …] …

[+ XTALK class]

[+ NONDEFAULTRULE ruleName]

[regularWiring] …

[+ SOURCE {DIST | NETLIST | TEST | TIMING | USER}]

[+ FIXEDBUMP]

[+ FREQUENCY frequency]

[+ ORIGINAL netName]

[+ USE {ANALOG | CLOCK | GROUND | POWER | RESET | SCAN | SIGNAL

| TIEOFF}]

[+ PATTERN {BALANCED | STEINER | TRUNK | WIREDLOGIC}]

[+ ESTCAP wireCapacitance]

[+ WEIGHT weight]

[+ PROPERTY {propNamepropVal} …] …

;] …

END NETS

|

| Figure-11: Net section of DEF file |

Summary: