Code: CDN4Y072021PD

Experience level: 4 Year

Profile: Physical Design Engineer

1. Introduction and physical design experience

2. What major differences have you observed in the 7nm and 14nm process nodes?

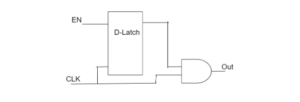

3. What is the functionality of this circuit? (He drawn schematic in paint)

4. Do you think, is there any issue with the above circuit? If so what would you suggest for improvement?

5. When clock gating circuit has added in the design RTL/Synthesis/PnR?

6. What are the checks you perform before starting the floor plan?

7. What is a library check?

8. What is the information available inside the .lib file?

9. How is the timing of a cell defined in .lib file?

10. What if the .lib file is missing but .lef file is available for a cell? and similarly, if .lef file is missing but .lib file is present for a cell?

11. How do we define the core area for any block?

12. How do we decide the height and width of a block?

13. What are the guidelines we need to follow in macro placement?

14. Is there any rule for abutting the macros?

15. What steps exactly tool does in the placement stage?

16. Why do we use boundary cells?

17. Why can’t we use placement blockage at the end of each row in place on the boundary cell?

18. What was the target latency in your block and what has been achieved?

19. Can you explain the ccopt method?

20. Which flavour of Vt cell you used in the clock tree?

21. Which type of derating you have been used in your different projects?

22. Why do we start using POCV when we had AOCV derate?

23. What is the shielding of a net? How it works?

24. Have you used shielding in your block?

25. What is NDR?

26. What is the difference between shielding and NDR? Can we use only one of these two?

27. Where did you placed the clock gating cell, near the sink or source?

28. Can you tell me the advantage and disadvantages of placing ICG near the sink and near the source?

29. What is CPPR?

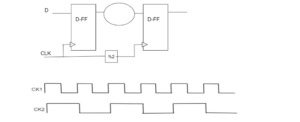

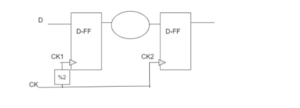

30. (A diagram has been drawn in paint as shown below) In this diagram can you tell me between which edges the setup and hold timing will be checked?

31. If we change the scenario like below, Now between which edge setup and hold will be checked?

32. What is internal power and switching power?

33. What is the impact of the threshold voltage of a cell on the internal power and switching power?

34. What is the impact of IR drop in cell delay?

35. How do you fix the static IR drop?

36. What was the limit of dynamic IR drop in your recent project?

Hello, thank you for the questions. Is there any place where I can find answers for these questions?

Hi ,

Let me post my answers:

2. Difference in DRC rules, IR will be more stringent and reduction in the channel width of MOS.

3.Integrated clock gate. Circuit is used for clock gating.

4. A negative triggered latch with enable circuit, in order to avoid glitch in clock width .

5. During synthesis , after the setup timing.

6.Check proper IP versions, constraints, proper blockages, proper upf , proper setup rows , understanding, data flow of the design, integration guidelines of any special analog hard IPs in the design

7.In library check, basically, we validate the libraries before starting the physical design by checking the consistency between the physical and logical library

8. lib is basically a timing model contains cell delays, transition, setup and hold time requirements

9.timing of the cell is defined in the forms of look up table. for example. O/p transition has look up table with inputs as i/p trans and o/p cap.

10. If .lef file is missing, the geometry of pins , must join pins, obstructions, grid info will be missing but we will have timing related to values of the cell, similarly without .lib cell may behave in abrupt manner as characterization is there for the delay values, but we will have floorplan ready with us without working .

11. A ‘core’ is the section of the chip where the fundamental logic of the design is placed

12. Several factors : Aspect ratio L:W Ideally should be close to 1. Less notches. Block boundaries shapes should be proper alignment with the logic requirement inside it.

13. Pin orientation towards blocks, proper channels between the hard macros for vdd and vss rails, should be placed closer to boundaries leaving space for cores

14. Yes, we can abutt macros in the orientation where logic is not travelling in between the macros . Also it depends on the other logic interacting to it. Grid spacing or Lego separation is another nice way to place the macro. It depends company to company.

15. Pre placements , spare cells placements , insertions of decaps, metal eco cells, magnet placements —> Legalisation –> Optimizing HFNS –> Remove existing buffer tress –> optimizing timing/power/congestion –> Scan chain reorderonng –> tie cells insertion –

16. To protect the gate of a standard cell placed near the boundary from damage during manufacturing., To avoid the base layer DRC (Nwell and Implant layer) at the boundary,To make the proper alignment with the other block.

17.Advanced nodes often requires the insertion of additional tap cells to manage the substrate and well noise. Before placing the standard cells we add boundary cells (Endcap cells) also, which are added to the ends of the cell rows and around the boundaries of objects such as core and hard macros and we checked that endcap cells are placed or not

18. 890..by adding and skewing the other edge to balence the treee. Custom clock tree construction

19.Innovus™ Clock Concurrent Optimization Technology with Stylus Common UI. :

Max traget trans , max fanout targets, max cap targets

20.It is just recommended not to fix different flavours of VT cells in CTS to avoid OCV variations

Please post the answers along with questions,so that it is easy to access.

Thank you