Once a chip is fabricated and if any functionality issue is found in the chip or some functionality enhancement is required in the next fabrication. This might be a very challenging task without spare cells. But with the help of pre-placed spare cells, these changes can be done very easily. In this article, we will discuss the spare cells in physical design.

Spare cells:

Spare cells generally consist of a group of standard cells mainly inverter, buffer, nand, nor, and, or, exor, mux, flip flops and maybe some specially designed configurable spare cells. Ideally, spare cells do not perform any logical operation in the design and act as a filler cell only. A group of spare cells is shown below.

The inputs of spare cells are tied either VDD or VSS through the tie cell and the output is left floating. Input can not be left floating as a floating input will be prone to get affected by noise and this could result in unnecessary switching in space cells which leads to extra power dissipation.

Use of Spare cells:

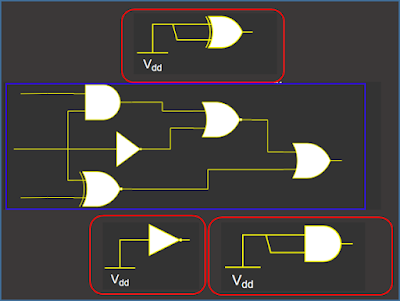

Spare cells enable us to modify/improve the functionality of a chip with minimal changes in the mask. We can use already placed spare cells from the nearby location and just need to modify the metal interconnect. There is no need to make any changes in the base layers. Using metal ECO we can modify the interconnect metal connection and make use of spare cells. We only need to change some metal mask, not the base layer masks.

For example, suppose in the above circuit we need to replace the last OR gate in the middle part of a circuit with an EXOR or an AND gate, we can reconnect the spare cell placed near this with metal ECO only.

Placement of Spare cells:

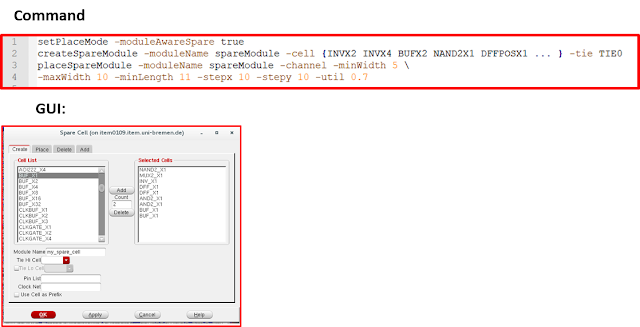

Spare cells can be added either by the netlist or by PnR tool command (or GUI too). In Physical design, we prefer to add the spare cells using tool command. These cells are added before the placement of standard cells throughout the design. The way of adding spare cells for Innovus and ICC tool has been explained below.

Innovus tool:

ICC tool:

Advantage and disadvantage of Spare cells:

Advantage:

Reusability:

There is only change in some metal and via masks, so base layers mask can be reused in chip fabrication.

Flexibility:

Small changes can be done in the design very easily.

Cost and Time saving:

We need only a few interconnect mask for a new design, which save lots of manufacturing cost for new chip fabrication. And using metal ECO we do not need to run full design cycle and therefore save design time.

Disadvantage:

Leakage Power:

Spare cells increase the leakage power dissipation in the design.

Area:

Spare cells cost extra area overhead in the design.

Thank You.

There are many different types of metal fabrication processes, each with its advantages and disadvantages. Some of the most common processes include