Standard cell library is an integral part of ASIC design flow and it helps to reduce the design time drastically. Standard cells used in the ASIC design is a part of a standard cell library along with some other file sets. In this article, we will discuss the important content inside the standard cell library and its uses.

Standard Cell Library:

Standard cell library is a collection of well defined and pre-characterized logic cells with multi-drive strength and multi-threshold voltage cells in the form of a predefined standard cell layout. It also contains a number of physical only cells and a set of library files required by Place and Route (PnR) tool for automatic placement and routing (APR).

Pre-characterization:

Before including a standard cell into standard cell library, the cells are gone through schematic design, simulations followed by Symbol creation, layout design (as per standard cells layout rules), physical verifications, abstraction, extraction and characterization. So the cells available in standard cell library are free from any DRC violations, well-characterized and suitable for PnR tool for automatic placement and routing.

Multi-drive strength cells:

A low drive strength cell will require less power and area but having more delay and more transition time whereas a high drive strength cell can drive a larger number of cells and having a fast transition. So as per the requirement, a PnR design engineer chooses the drive strength of cells to optimize the area, power and performance.

Multi-Vt cells:

A low threshold voltage (LVT) cell will have a lesser delay but higher leakage power as compared to a high threshold voltage (HVT) cell. So as per the requirement of timing and power a PnR engineer uses HVT and LVT cell to balance the power and timing of the design. There is no difference in the area on multi-Vt cells. A modern standard cell library contains generally ULVT, LVT, SVT, HVT types of cells in which Vt is in increasing order.

Physical only cells:

In physical design, We need to add a variety to standard cells to mitigate various effects and manufacturing issues. These cells do not have any logical functions. For example to overcome the latch-up issue we need to add well tap cells. Decap cells, endcap cells, antenna cells and filler cells are the example of such cells.

In the next section, we will discuss various cells collection and standard cells library and the set of important files.

Cell Collections:

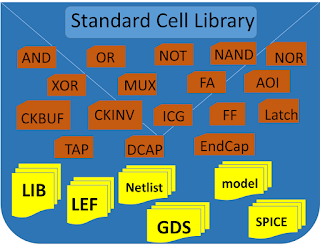

In general, a standard cell library contains the following types of cell:

- All basic and universal gates (like AND, OR, NOT, NAND, NOR, XOR etc)

- Complex gates (like MUX, HA, FA, Comparators, AOI, OAI etc)

- Clock tree cells (like Clock buffers, clock inverters, ICG cells etc)

- Flip flops and latches

- Delay cells

- Physical only cells

- Scannable Flip flops

File Collections:

Apart from the standard cells, Standard cell library is delivered with a collection of files which contains all the information required to auto place and route. These files are mainly:

- LIB files (.lib)

- LEF files (.lef)

- Netlist file (.v )

- GDS file (.gds)

- SPICE Netlist (.sp)

- Model file (.m)

All the format of files mentioned here with the reference of the Cadence tool. Some files format is different in the Synopsys tool but the information inside the file is the same. Brief information of these files is given below. Detailed information of all these files can be found in the “File in VLSI” section of this blog.

Timing library (LIB or DB) files are generated during the characterization of cells. Library files contain cell delay, power and area information. Physical library (LEF) file is an abstract view of the layout of the cells. LEF file contains the information of cell boundary, Pins inside the cell, location, direction, and metal layer of each pin. Netlist file is a Verilog file of the standard cell which defines the functionality of a cell. GDS file is the layout of the standard cell. SPICE netlist is the netlist of cell in SPICE format is used for simulation. Model file contains the various design parameters of the cell required for SPICE simulation.

Thank you.

Hi sir, What happens during characterization of standard cells?. How this process goes?. Can you please share something about it?.

Hi,

Characterization is the process where the test chip is being probed in a probe station and majored its various characteristics (like delay, power, capacitances, on current, off current and many more)under various conditions. And these data is made available in your standard cell library so that during a PnR and signoff we can estimate the timing, power etc.

Hi Sir,What are the various design parameters of the cell required for SPICE simulation.

Hi,

It would require transistors gate length, width, oxide thickness, operating voltage and temperature.

Model file of the tr. will take all these input and based on the functions defined in model file, tool will calculate the currents and delays.